Grabador ISP simple por puerto paralelo, para los AT89S51, AT89S52 ...

http://grabador-isp-atmel.blogspot.com/

Grabador, programador de Atmel serie 89 AT89C51 /52 /55 y los At89S51/52/55 ...

http://www.grabador-atmel.blogspot.com/

Programacion del pic17f877A

http://www.programacion-pic16f877a.es.tl/

martes, 26 de agosto de 2008

domingo, 24 de febrero de 2008

PROGRAMACION DEL AT89C52

Todos los modelos de la familia 51 ejecutan cl mismo conjunto de instrucciones. Estas instrucciones estan optimizadas para cl control de aplicaciones en 8 bits. Estan provistas de una buena variedad de modos de direccionamiento para acceder a la memoria RAM de datos internos del microcontrolador, facilitando operaciones del tipo byte sobre una pequeña estructura de datos. Permiten la manipulacion directa de control y procesamiento booleano de estructuras de datos del tamaño de un bit. En esta breve introduccion se estudiaran los modos de direccionamiento y el juego de instrucciones agrupadas por especialidades de esta manera:

· Instrucciones aritmeticas.

· Instrucciones logicas.

· Instrucciones para la transferencia de datos en:

a) RAM interna.

b) RAM externa.

· Instrucciones para cl tratamiento de tablas.

· Instrucciones booleanas.

· Instrucciones de salto.

MODOS DE DIRECCIONAMIENTO

Direccionamiento Directo

El operando se especifica en la instruccion por un campo de direccion de 8 bits. Solo la RAM interna de datos (primeros 128 bytes) y la zona de SFR se pueden direccionar de esta forma.

ejemplo: ADD A,38H; es decir, suma (ADD) el contenido del acumulador (A) con el contenido de

la posicion de memoria (38):

la posicion de memoria (38):

Direccionamiento Indirecto

La instruccion especifica un registro que contiene la direccion del operando. Tanto la memoria RAM interna (256 bytes/128 bytes) como la externa se pueden direccionar indirectamente.

Los registros para direccionar sobre el mapa de 8 bits pueden ser el R0 y R1 del banco de registros seleccionado, o el Stack Pointer. El registro para direccionar sobre 16 bits solo puede ser el Puntero de Datos (Data Pointer = DPTR).

Ejemplo: ADD A,@R0 ; Asi, si (RO)=38H la operaci6n sera: A << (A) + (38) Igual que en el ejemplo anterior (@) es el identificador del direccionamiento indirecto.

Direccionamiento por registro

Los Microcontroladores 8052/8051, como se ha visto, contiene cuatro bancos de registros seleccionados por los bits 3 y 4 del PSW, y cada banco de registros tiene ocho registros del RO al R7 (vease Apartado 2.5). El propio codigo de operacion de la instruccion especifica con que registro se opera; es decir, cuando la i nstru ccion es ejecutada se accede a u no de los 8 reg istros del banco seleccionado.

Ejemplos:

MOV Rn,A ; operación: (Rn) << (A) MOV Rn,#dato; operación (Rn) << (#dato)

MOV Rn,A ; operación: (Rn) << (A) MOV Rn,#dato; operación (Rn) << (#dato)

Direccionamiento implicito

Algunas instrucciones especifican, implicitamente, el registro sobre el que van a operar, como el acumulador, el puntero de datos, etc. No necesitan especificar el operando porque esta implicito en el codigo de operacion.

ejemplos:

INC A ; Incrementa el contenido del acumulador: A << (A) + 1 INC DPTR ; Incrementa puntero de datos: DPTR << (DPTR) + 1

Direccionamiento inmediato

Al codigo de operacion le sigue una constante en la memoria de programas.

Ejemplo:

MOV A, #255 ; Carga en el acumulador el numero decimal 255.

en hexadecimal: MOV A, #FFH MOV A, #11111111B ó en binario:

MOV A, #255 ; Carga en el acumulador el numero decimal 255.

en hexadecimal: MOV A, #FFH MOV A, #11111111B ó en binario:

Direccionamiento indexado

Este direccionamiento solo es posible en la memoria de programas y solo permite la lectura. Es utilizado para la lectura de tablas. Un registro base de 16 bits (cl DPTR o cl contador de programa) apunta a la base de la tabla y cl contenido del acumulador es cl offset que permite acceder a la lectura de esa posicion de la tabla. Es decir, la direccion de la tabla que se va a acceder esta formada por la suma del acumulador y cl puntero base.

Se puede utilizar otro tipo de direccionamiento indexado en las instrucciones de salto. En este caso la direccion de destino del salto se calcula como la suma del puntero base y cl dato del acumulador.

Se puede utilizar otro tipo de direccionamiento indexado en las instrucciones de salto. En este caso la direccion de destino del salto se calcula como la suma del puntero base y cl dato del acumulador.

CICLO DE INSTRUCCION

La ejecucion de un ciclo de instruccion comienza en cl estado 1 del ciclo maquina, cuando cl codigo de operacion es almacenado en cl Registro de Instruccion. (Para comprender este apartado tener a la vista la Figura 3.1 y la Tabla 4.5, Set de Instrucciones. )

Como norma general, una instruccion requiere de uno q mas ciclos maquina, en funcion de:

a) El codigo de operacion

Por ejemplo, la instruccion INC A (Figura 3.1 A) tiene 1 byte de instruccion y requiere 1 ciclo maquina, la instruccion INC DPTR, tambien, de 1 byte de instruccion requiere de 2 ciclos maquina (Figura 3.1 C) y la instruccion MUL AB requiere de 4 ciclos maquina para su total ejecucion y ocupa 1 byte en la memoria.

b) El numero de bytes

Por ejemplo, la instruccion MOV A, #data tiene 2 bytes de instruccion y requiere de 1 ciclo maquina (Figura 3.1 B). En cambio la instruccion MOV direct, # data al constar de 3 bytes necesita de 2 ciclos maquina. Esto no ocurre siempre, es decir, a mas bytes mas ciclos maquina, como puede verse en la Figura 3.1 B correspondiente a la instruccion MOV A, #data y en la Figura 3.1 D MOVX A,@Ri, la primera instruccion tiene 2 bytes y la segunda solo 1. en cambio la primera requiere 1 ciclo maquina y la segunda 2.

Ante la imposibilidad de establecer una norma o regla que facilite cl conocimiento del numero de bytes y ciclo de instruccion se ha editado la Tabla 4.5 con el set completo de instrucciones. Cabe destacar, tambien, en la Figura 3.1, que en cada ciclo maquina se producen 2 accesos a la memoria, cl primero, si es comienzo de ciclo de instruccion, siempre leera cl codigo de operacion, cl segundo, que normalmente se descarta, se utiliza para leer cl segundo byte, operando de la instruccion, como ocurre en la Figura 3.1 B.

TIPOS DE INSTRUCCIONES

El set de instrucciones del 8052/8051 se puede dividir segun las especialidades:

· Instrucciones aritmeticas.

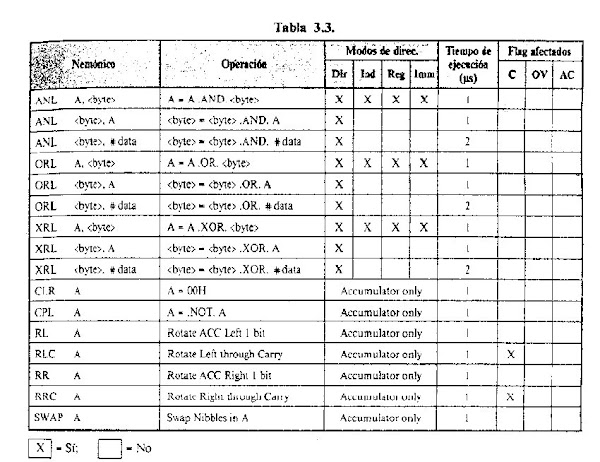

· Instrucciones logicas.

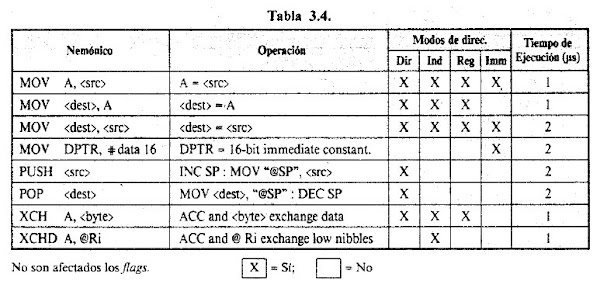

· Instrucciones de transferencia de datos.

· Instrucciones booleanas

· Instrucciones de salto.

Suscribirse a:

Entradas (Atom)